应用文章

产品推荐

应用文章

提高电子模块抗脉冲干扰能力

- 发布时间:2018-10-17 16:02:18

在抗扰度试验中,与在低电源压操作精密的集成路复杂模块正逐渐变得显而易见。因此,在电子系统中开发人员实现了一列应对变得显而易见。因此,在电子系统中开发人员实现了一列应对变得显而易见。因此,在电子系统中开发人员实现了一列应对措施,旨在保证高抗扰度。但是,如果他们从假设的干扰耦合路径知识得到EMC措施才能取得成功。由于每一个新开发的电子模块可能包括基误解风险,在实验由于每一个新开发的电子模块可能包括基误解风险,在实验中验证所有选择是非常有用的。

如果一个现代电子模块将被开发为包括这样的特性:

• 高抗干扰度

• 没有屏蔽外壳

• 低电流输入

其电磁稳定性将取决于所使用的子路和环境(布局)特性。

工程师会发现它难以评价一个新的开发阶段的规划所采取任何措施的规划所采取任何措施EMC。任何新的开发受到制约的假设而不是因为在电路选择的EMC特性很少事实的信息可以用。所使电路的EMC参数越精确,开发人员的EMC决定将更准确。当今这些参数是容易确定的,得益于特殊的IC测量技术。如果计划的一系列大小并不能证明IC测试的成本,在开发使用过程中测试局部样品模块中的潜在敏感设备是经典方法。

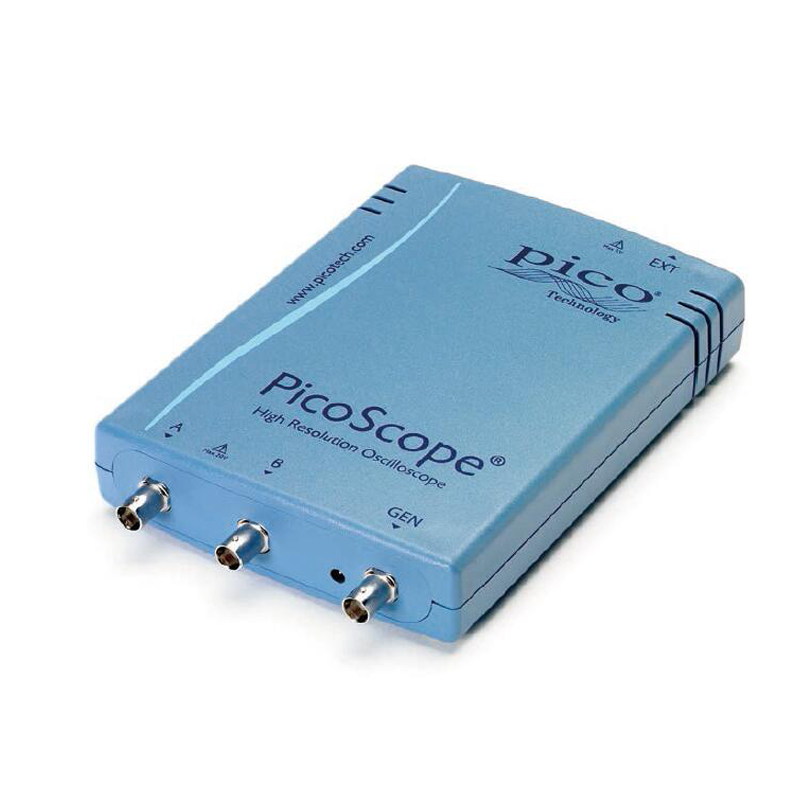

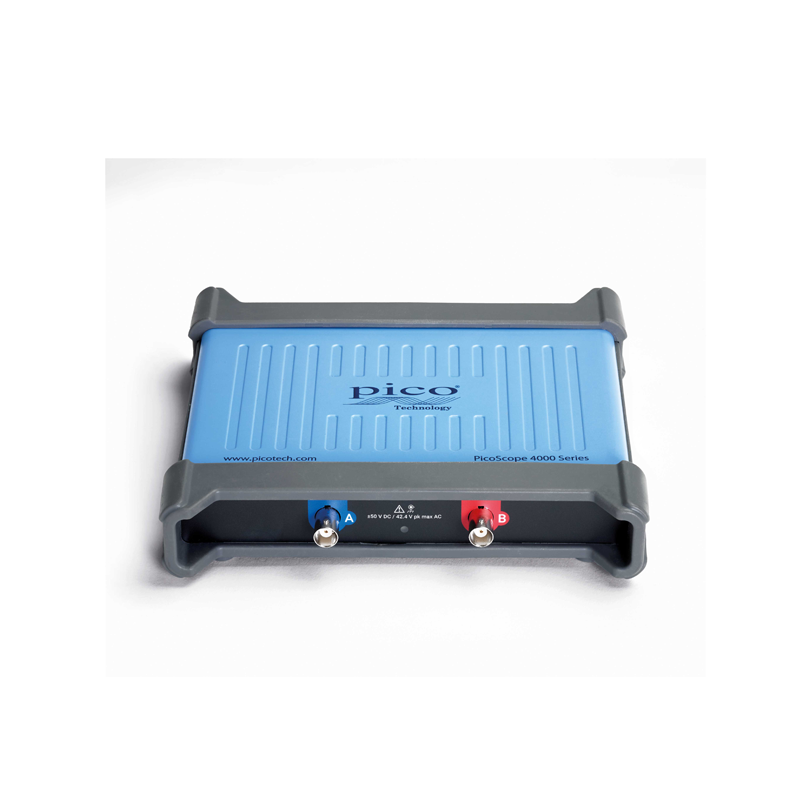

组合使用的脉冲群发生器与场源,传感和探针已经成功证明在开发过程中电子模块的脉冲群和ESD测试是有效的。以下描述了一种用于在开发过程中测试模块以确定到现在都难以分析干扰现象

1)向更高抗扰度的步骤

根据IEC61000-4-4标准,模块的抗扰度测试是我们检测的起点。在标准合规测试中,由脉冲群发生器产的干扰耦合到外壳或供电线。通过装置模块流动的脉冲状干扰的路径是未知的。

在装置中,这些干扰未知的成分符合未知敏感设备,并产生一个功能故障。这个敏感点一般都可以精确定位至几平方厘米的模块,但不能由一般都可以精确定位至几平方厘米的模块,但不能由合规测试进行定位。在没有进一步与模块干扰的电路中,即使在没有进一步与模块干扰的电路中,即使开发人员成功地测量干扰电流,它开发人员成功地测量干扰电流,它仍然是不清楚多少干扰电流的路可以不允许在各个引脚。开发人员还不知道在哪里与其连接的干扰电流磁场在在导体环路感应出电压脉冲或耦合电场电容进入易敏感的线路。关于出现故障模式的准确信息在失败的合规测试中是一个的决定性结果。在进一步的开发中,这允许开发人员借鉴如何在模块上继续测试。

如果在布局更精确地分离敏感点的相采取EMC措施,任何的成功将在很大任何的成功将在很大程度上是机会的问题。间接补救行动(屏蔽板,过滤器改变了间接补救行动(屏蔽板、过滤器改变了星形接地系统、电气隔离等)经常在故障位置来解决这个问题。

更多详细资料,请下载:![]() 提高电子模块抗脉冲干扰的能力中文版本.pdf

提高电子模块抗脉冲干扰的能力中文版本.pdf

版权声明:本资料属于北京海洋兴业科技股份有限公司所有,如需转载,请注明出处!

QQ客服

QQ客服